手机访问更快捷

安卓版

营销推广更便捷

手机访问更快捷

安卓版

营销推广更便捷

我们在SOA/RSOA/SLD的ASE(放大的自发辐射)光谱测试中,经常会观察到光谱中有周期性的变化,通常我们称之为纹波。在实际应用中,我们大多不希望这些纹波的存在。

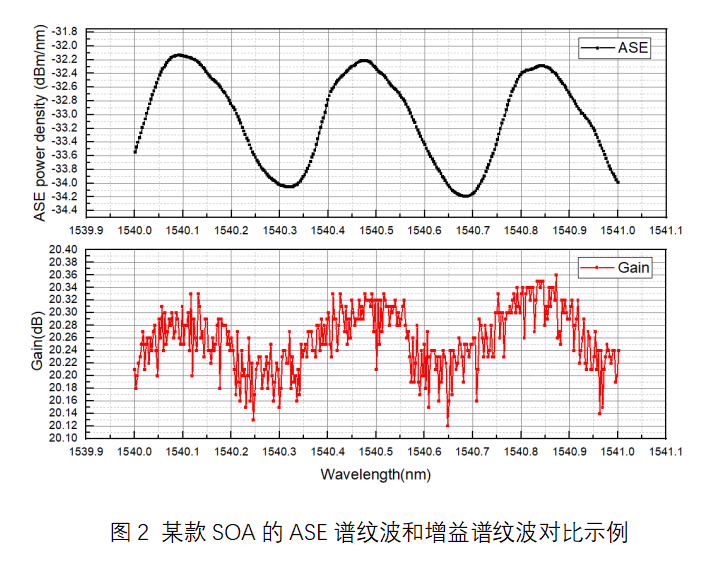

在SOA/RSOA的使用时,ASE光谱比较容易测量,增益谱测量则比较复杂。图2是我们对同一个SOA器件做的ASE谱和增益谱的对比测试(注:增益谱中的快速变化是测量误差),可以看到增益谱的纹波与ASE谱的纹波波形和周期一致,但增益谱纹波明显小于ASE谱纹波,图2中ASE纹波约为2dB,增益谱纹波0.2dB。尽管幅度差异较大,但由于ASE光谱测量的简便性,我们仍可以使用ASE谱纹波来快速评估增益谱纹波。

纹波与端面反射率及增益直接相关。激光振荡条件为(GsR)2=1,其中Gs为单程增益,R代表端面反射率,为了避免激光振荡,应尽可能减少光反射回有源区域,如果反射率不够低,则在增益谱中会观察到纹波。

如上面公式,纹波深度m是前后端面反射率R1,R2和单程增益Gs的函数。例如,当R1和R2为10-4,Gs为20dB时,m=0.09dB。根据公式,减小纹波的方法就是减少增益和端面反射率。使用SOA时则可通过减小偏置电流方式来减小增益,但通常的应用中,我们需要较高的增益,因此在实际设计中,就只有一个方式就是尽可能减少端面反射率,通常需要<10-4。

除了芯片本身的端面发射外,芯片的封装,以及SOA的使用不当也会带来纹波或激射。

1.芯片设计

SOA设计中一定要尽量减少光反射到有源区域,通常应<10-5。如果反射率不够低,则在增益谱中会观察到纹波。当纹波深度大于3dB时,此时通常被称为FP光放大器。尽管腔谐振可以增强小信号增益,但端面反射通常会影响SOA的性能。谐振波长的波动导致信号增益的变化。此外,过大的端面反射率会降低载流子密度、增益带宽和输出饱和功率,并提高噪声系数。

有多种芯片设计方法可以减少腔体谐振,这些方法相互组合可以实现更低反射率。

1)在芯片端面上使用抗反射涂层ARC,当具有适当厚度和折射率的介电材料层沉积到器件面上时,会形成滤光,适当设计的多层AR涂层可以在较宽的带宽上产生低至10-3的反射率。ARC涂层同样可以降低耦合输入损耗,并改善噪声系数。

2)倾斜有源波导,使得光被反射远离有源区。Zah等人在1987年采用了斜波导,角度通常在5°到10°之间,与偏振无关,可以在大波长范围内将反射率降低10-4以下。随着倾角的增加,远场不对称性开始降低与光纤的耦合效率。因此,理想倾斜角度在7-10度之间。

3)使用锥形波导变细或使用窗口区域(即在端面之前终止波导),以便使模式轮廓扩展。以这种方式,仅光场的少部分被反射回有源区域。

在商用品中,通常采用斜波导和AR涂层组合的方式,这既降低了涂层公差要求,又确保了10-5量级的低反射率,以确保增益波纹保持在1dB以下。

2.封装设计

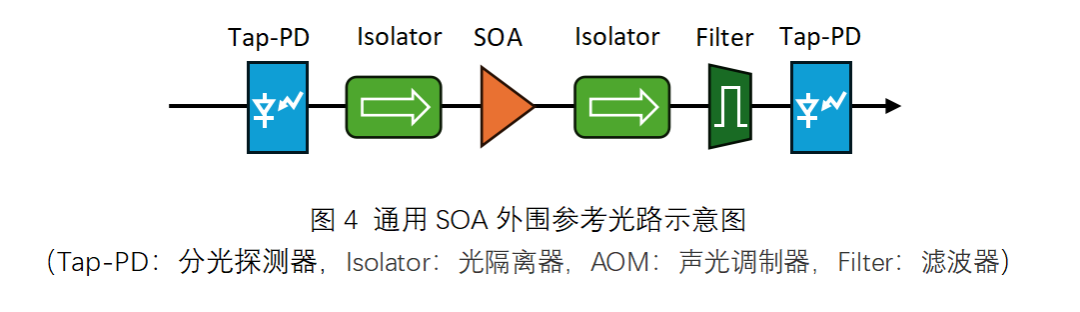

封装中避免光路中的反射可减少封装带来的纹波效应,耦合时注意避免在芯片、透镜、准直器、隔离器、光纤端面上形成FP腔,芯片和透镜等应镀有对应波长的增透膜。

3.SOA的使用

(摘自华莱光电公众号)

从下图实测的VCSEL光谱图来看,主峰包络上出现了明显的周期性调制结构(干涉条纹样的波动),这是典型的干涉条纹叠加现象。

【观察特征】

·测量范围为 1.0 nm(从 1541.726 nm 到 1542.726 nm)

·中心波长约 1542.2 nm

·在主峰顶和左右边沿区域均有周期性振荡调制

·周期约为 0.1 nm

【可能成因分析】

光路中存在反射面干涉(常见)

如:光纤端面? VCSEL 芯片 ? 透镜等形成虚拟 Fabry-Pérot 腔。

【成因可能】

①光路中存在多余反射面,形成干涉腔

·如 VCSEL 芯片与 collimator、尾纤、连接器、测试光纤末端之间形成虚拟 FP腔

·多个面之间的微小反射叠加会导致拍频干涉(modulation on envelope)

·用之前公式估算(周期≈ 0.1 nm)

·条纹周期 Δλ 与腔长 L 的关系:

Δλ≈λ2/(2nL)

例如波长为 1542 nm,干涉周期为 0.1 nm,计算可得腔长约:

L=λ2/(2nΔλ )=15422/(2*1.45*0.1)≈8.2mm

·表明可能是光纤、准直透镜之间,或是器件封装内的反射造成的。

·表明这个调制来自一个约 8 mm 的光学路径反射腔,很可能是光纤端面 ? 激光器? collimator 之间。

②VCSEL结构本身的腔内多模干涉

·如果是多纵模激射,也可能产生频谱上的拍频调制。

·但这种调制往往在频率上不这么规律、对称,图中更像是外腔干涉造成的清晰周期结构。

③测试平台反射干扰

·光谱仪输入端或尾纤反射回波造成反馈干涉。

特别是若使用FC/PC 连接器,建议用 FC/APC 斜面尾纤进行验证。

【总结判断】

从图上看,干涉条纹清晰、等间距、周期性良好,更倾向于是测量系统中的 FP 反射形成的干涉条纹,不是激光器本身的固有模式结构,而是外腔干涉造成的调制现象,源头可能是尾纤、准直透镜与器件之间形成了反射腔。优化耦合光路(隔离+斜面+减少反射面)后再测,基本可以消除这个条纹调制。

注:本文由天津见合八方光电科技有限公司撰写,旨在推广和分享相关半导体光放大器SOA基础知识,助力SOA技术的发展和应用。

天津见合八方光电科技有限公司是一家专注国产半导体光放大器SOA研发和生产的高科技企业,目前已推出多款半导体光放大器SOA产品(850nm,1060nm,1270nm,1310nm, 1550nm,1625nm)以及增益芯片RSOA产品(850nm,1310nm,1550nm),公司已建立了万级超净间实验室,拥有较为全面的光芯片的生产加工、测试和封装设备,并具有光芯片的混合集成微封装能力。目前公司正在进行NLL/ECL+SOA的混合集成器件、大功率SOA器件的研发工作,并可对外承接各种光电器件测试、封装和加工服务。